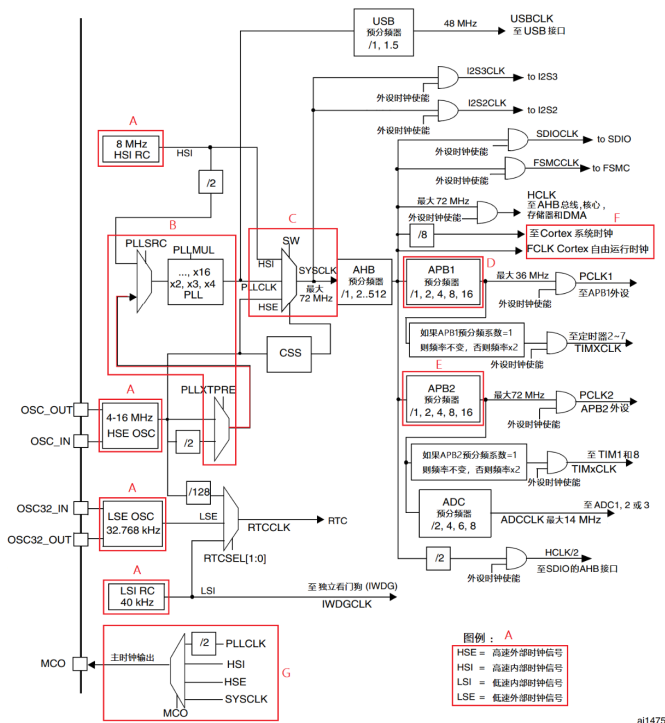

时钟树

系统时钟配置

配置HSE_VALUE

在stm32f1xx_hal_conf.h文件中设置外部晶振频率

#if !defined (HSE_VALUE)

#define HSE_VALUE 8000000U /*!< Value of the External oscillator in Hz */

#endif /* HSE_VALUE */

#if !defined (HSE_STARTUP_TIMEOUT)

#define HSE_STARTUP_TIMEOUT 100U /*!< Time out for HSE start up, in ms */

#endif /* HSE_STARTUP_TIMEOUT */

选择时钟源,配置PLL

通过HAL_RCC_OscConfig()函数配置

HAL_StatusTypeDef HAL_RCC_OscConfig(RCC_OscInitTypeDef *RCC_OscInitStruct);该函数只有一个形参,就是结构体 RCC_OscInitTypeDef 类型指针。接下来我们看看结构体

RCC_OscInitTypeDef 的定义:

RCC_OscInitTypeDef rcc_osc_init = {0};

rcc_osc_init.OscillatorType = RCC_OSCILLATORTYPE_HSE; /* 选择要配置 HSE */

rcc_osc_init.HSEState = RCC_HSE_ON; /* 打开 HSE */

rcc_osc_init.HSEPredivValue = RCC_HSE_PREDIV_DIV1; /* HSE 预分频系数 */

rcc_osc_init.PLL.PLLState = RCC_PLL_ON; /* 打开 PLL */

rcc_osc_init.PLL.PLLSource = RCC_PLLSOURCE_HSE; /* PLL 时钟源选择 HSE */

rcc_osc_init.PLL.PLLMUL = RCC_PLL_MUL9; /* PLL 倍频系数 */

if (HAL_RCC_OscConfig(&rcc_osc_init) != HAL_OK)/* 初始化 */

{

Error_Handler();

}选择系统时钟源

通过HAL_RCC_ClockConfig()函数配置

HAL_StatusTypeDef HAL_RCC_ClockConfig(RCC_ClkInitTypeDef *RCC_ClkInitStruct,

uint32_t FLatency);该函数有两个形参

第一个形参 RCC_ClkInitStruct 是结构体RCC_ClkInitTypeDef 类型指针变量,用于设置 SYSCLK 时钟源以及 SYSCLK、 AHB、 APB1 和 APB2 的分频系数。

第二个形参 FLatency 用于设置 FLASH 延迟。

RCC_ClkInitTypeDef 结构体类型定义比较简单,我们来看看其定义:

RCC_ClkInitTypeDef rcc_clk_init = {0};

/* 选中 PLL 作为系统时钟源并且配置 HCLK,PCLK1 和 PCLK2;表示我们要配置的是 SYSCLK、 HCLK、 PCLK1 和 PCLK 四个

时钟*/

rcc_clk_init.ClockType = (RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK

| RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2);

rcc_clk_init.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;/* 设置系统时钟来自 PLL */

rcc_clk_init.AHBCLKDivider = RCC_SYSCLK_DIV1; /* AHB 分频系数为 1 */

rcc_clk_init.APB1CLKDivider = RCC_HCLK_DIV2; /* APB1 分频系数为 2 */

rcc_clk_init.APB2CLKDivider = RCC_HCLK_DIV1; /* APB2 分频系数为 1 */

/* 同时设置 FLASH 延时周期为 2WS,也就是 3 个 CPU 周期。 */

if (HAL_RCC_ClockConfig(&rcc_clk_init, FLASH_LATENCY_2) != HAL_OK)

{

Error_Handler();

}

PLL 时钟为 PLLCLK = HSE * 9 = 8MHz * 9 = 72MHz。同时我们选择系统时钟源为 PLL,所以系统时钟 SYSCLK=72MHz。

AHB 分频系数为 1,故频率为 HCLK=SYSCLK/1=72MHz。

APB1 分频系数为 2,故其频率为 PCLK1=HCLK/2=36MHz。

APB2 分频系数为 1,故其频率为 PCLK2=HCLK/1=72MHz。

Comments NOTHING